# 1/3.6 inch 1.5Mega Single Chip CMOS Image Sensor with 1440 X 1024 Pixel array

### PO1150K

6<sup>th</sup> Floor, Gyeonggi R&DB Center, 906-5 lui-dong, Yeongtong-gu, Suwon-si, Gyeonggi-do, 443-766, Korea Tel: 82-31-888-5300, FAX: 82-31-888-5398

> Copyright © 2010, Pixelplus Co.,Ltd ALL RIGHTS RESERVED

### 1/3.6 inch 1.5Mega Single Chip CMOS Image Sensor with 1440 X 1024 Pixel array

#### Features

- ▶ 1456 x 1040 effective pixel array with RGB Bayer color filters and micro-lens

AVDD: 2.8V, DVDD: 1.8V

HVDD: 1.8 ~ 3.3V

- Output formats

CCIR656, 8bits YCbCr422,

8bits RGB Bayer, RGB565, RGB444,

8bits Mono,10bits Raw Bayer

- ▷ Image processing on chip Lens shading, Gamma correction, Defect correction, Low pass filter, Color interpolation, Edge enhancement, Color correction, Brightness, Contrast, Saturation, Auto black level compensation, Auto white balance, Auto exposure control and Back light compensation. Special effect (Reverse, Sketch, Sepia, Embossing, Black & White)

- Frame size, window size and position can be programmed through a 2-wire serial interface bus

- High Image Quality and High low light performance

- Shutter type : ERS (Electrical Rolling Shutter)

- Scan mode : Progressive Scan

- Down scaling supports x1/8 ~ x1 : 1/32 steps for X, Y respectively

- Support 1280x720 Bayer image size, for High Definition (HD) 15 fps video systems

- Support 720x480p YUV 30 fps for D1 systems

- On-chip phase locked loop (PLL)

- Off-chip IR-LED control

- ▷ CSP/CLCC/PLCC Package type supports

| AGND 42 | AVDD  | ATES | ISIN | STDBY | RSTB | VSYNC | D9 | D8   | D7      | DVDD | DGND | D6      | D5      | HVDD    | SSDA | SSCL     | CADDR1 | DVDD | DGND    | SGND      |

|---------|-------|------|------|-------|------|-------|----|------|---------|------|------|---------|---------|---------|------|----------|--------|------|---------|-----------|

| 42      | 41    | 40   | 39   | 38    | 37   | 36    | 35 | 34   | 33      | 32   | 31   | 30      | 29      | 28      | 27   | 26       | 25     | 24   | 23      | 22        |

|         |       |      |      |       |      |       |    |      |         |      |      |         |         |         |      |          |        |      |         |           |

|         |       |      |      |       |      |       |    | F    | 0       | 11!  | 50I  | <       |         |         |      |          |        |      |         |           |

|         |       |      |      |       |      |       |    |      |         |      |      |         |         |         |      |          |        |      |         |           |

| _       | 2     | ω    | 4    | O1    | 6    | 7     | 00 | 9    | 10      | 11   | 12   | 13      | 14      | 15      | 16   | 17       | 18     | 19   | 20      | 21        |

| AGND1   | AVDD1 | Ξ    | DO   | 9     | D2   | D3    | D4 | DVDD | 10 DGND | ×    | X2   | 13 HVDD | 14 PCLK | 15 DGND | DVDD | 17 HSYNC | DGND   | LED0 | 20 LED1 | 21 CADDR0 |

[Fig. 1] PIN Description

| Effective Pixel Array    | 1456(H) x 1040(V)                                                                                  |  |  |  |  |  |  |  |

|--------------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pixel Size               | 2.8 um x 2.8 um                                                                                    |  |  |  |  |  |  |  |

| Effective Image Area     | 4.0768 mm x 2.912 mm                                                                               |  |  |  |  |  |  |  |

| Optical Format           | 1/3.6 inch                                                                                         |  |  |  |  |  |  |  |

| Max. Clock frequency     | 48 MHz                                                                                             |  |  |  |  |  |  |  |

| Max. Frame Rate          | 15 fps @ YUV, 1440x1024, 48MHz<br>15 fps @ Bayer, 1440x1024, 48MHz<br>30 fps @ YUV, 720x480, 48MHz |  |  |  |  |  |  |  |

| Dark Signal              | 15.5 [mV/sec] @ 60°C                                                                               |  |  |  |  |  |  |  |

| Sensitivity              | 1.33 [V/Lux.sec]                                                                                   |  |  |  |  |  |  |  |

| Power Supply             | Analog : 2.8V, Core : 1.8V<br>IO : 1.8V ~ 3.3V                                                     |  |  |  |  |  |  |  |

| Power Consumption        | 159.2 [mW] @ Dynamic                                                                               |  |  |  |  |  |  |  |

| Power Consumption        | 15 [uW] @ Standby                                                                                  |  |  |  |  |  |  |  |

| Operating Temp.          | - 40 ~ 105 [°C] @ AT                                                                               |  |  |  |  |  |  |  |

| (Fully Functional Temp.) | - 30 ~ 80 [°C] @ CT                                                                                |  |  |  |  |  |  |  |

| Dynamic Range            | 66.7 [dB] @ 30 fps                                                                                 |  |  |  |  |  |  |  |

| SNR                      | 42 [dB]                                                                                            |  |  |  |  |  |  |  |

[Table 1] Typical Parameters

## 1/3.6 inch 1.5Mega Single Chip CMOS Image Sensor with 1440 X 1024 Pixel array

#### Signal Environment

PO1150K has 3.3V tolerant Input pads. Input signals must be higher than or equal to HVDD but cannot be higher than 3.3V. PO1150K input pad has built in reverse current protection circuit, which makes it possible to apply input voltage even if the HVDD is disconnected or floating. Voltage range for all output signals is 0V ~ HVDD.

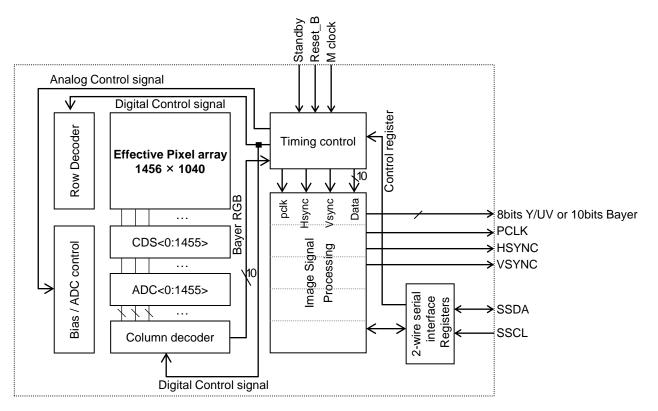

#### Chip Architecture

PO1150K has 1456 x 1040 effective pixel array and column/row driver circuits to read out the pixel data progressively. CDS circuit reduces noise signals generated from various sources mainly resulting from process variations. Pixel output is compared with the reset level of its own and only the difference signal is sampled, thus reducing fixed error signal level. Each of R, G, B pixel output can be multiplied by different gain factors to balance the color of images in various light conditions. The analog signals are converted to digital forms one line at a time and 1 line data are streamed out column by column. The Bayer RGB data are passed through a sequence of image signal processing blocks to finally produce YCbCr 4:2:2 output data. Image signal processing includes such operations as gamma correction, defect correction, low pass filter, color interpolation, edge enhancement, color correction, contrast stretch, color saturation, white balance, exposure control and back light compensation. Internal functions and output signal timing can be programmed simply by modifying the register files through 2-wire serial interface.

[Fig. 2] Block Diagram